What Is Difference Between Datapath And Control Path

8 Execution of a Complete Educational activity – Datapath Implementation

Dr A. P. Shanthi

The objectives of this module are to discuss how an instruction gets executed in a processor and the datapath implementation, using the MIPS architecture equally a case study.

The characteristics of the MIPS compages is first of all summarized beneath:

• 32bit byte addresses aligned – MIPS uses 32 bi addresses that are aligned.

• Load/store just displacement addressing – It is a load/store ISA or register/register ISA, where only the load and store instructions employ memory operands. All other instructions use only register operands. The addressing style used for the retentivity operands is displacement addressing, where a displacement has to exist added to the base of operations annals contents to get the constructive address.

• Standard information types – The ISA supports all standard data types.

• 32 GPRs – There are 32 full general purpose registers, with register R0 e'er having 0.

• 32 FPRs – There are 32 floating bespeak registers.

• FP status annals – There ia floating point status register.

• No Condition Codes – MIPS architecture does not support condition codes.

• Addressing Modes – The addressing modes supported are Immediate, Deportation and Annals Fashion (used just for ALU)

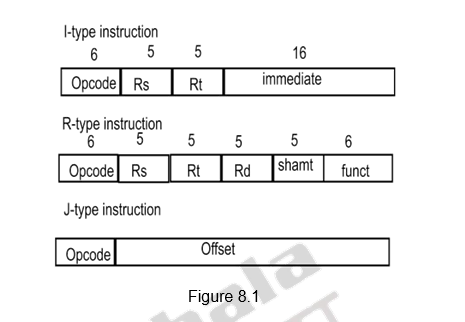

3 fixed length formats – There are three 32-bit instruction formats that are supported. They are shown below in Figure viii.1.

Nosotros will examine the MIPS implementation for a elementary subset that shows most aspects of implementation. The instructions considered are:

- The memory-reference instructions load word (lw) and shop word (sw)

- The arithmetic-logical instructions add, sub, and, or, and slt

- The instructions co-operative equal (beq) and spring (j) to exist considered in the end.

This subset does not include all the integer instructions (for instance, shift, multiply, and dissever are missing), nor does it include any floating-point instructions. Even so, the key principles used in creating a datapath and designing the control will be illustrated. The implementation of the remaining instructions is similar. The key design principles that we have looked at earlier can be illustrated by looking at the implementation, such as the common guidelines, 'Make the common case fast' and 'Simplicity favors regularity'. In improver, most concepts used to implement the MIPS subset are the aforementioned basic ideas that are used to construct a wide spectrum of computers, from loftier-operation servers to general-purpose microprocessors to embedded processors.

When we await at the instruction cycle of whatever processor, it should involve the following operations:

- Fetch instruction from memory

- Decode the education

- Fetch the operands

- Execute the education

- Write the effect

Nosotros shall look at each of these steps in particular for the subset of instructions. Much of what needs to be washed to implement these instructions is the same, contained of the verbal class of pedagogy. For every instruction, the first two steps of pedagogy fetch and decode are identical:

- Send the program counter (PC) to the program retentivity that contains the lawmaking and fetch the instruction

- Read one or 2 registers, using the register specifier fields in the educational activity. For the load word didactics, nosotros need to read simply i register, but most other instructions require that we read 2 registers. Since MIPS uses a stock-still length format with the register specifiers in the aforementioned identify, the registers tin can be read, irrespective of the instruction.

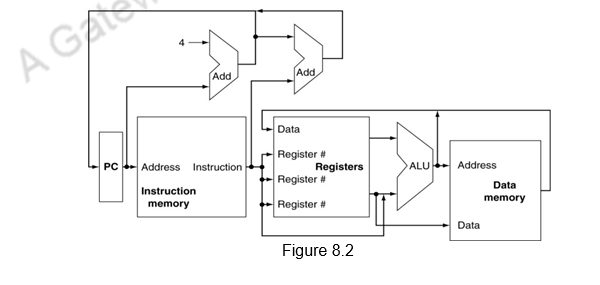

After these ii steps, the actions required to complete the instruction depend on the type of instruction. For each of the three teaching classes, arithmetic/logical, retentiveness-reference and branches, the actions are more often than not the aforementioned. Even across different instruction classes there are some similarities. For example, all instruction classes, except bound, use the arithmetics and logical unit, ALU after reading the registers. The load / store memory-reference instructions use the ALU for effective address calculation, the arithmetic and logical instructions for the functioning execution, and branches for condition evaluation, which is comparison here. Every bit we can come across, the simplicity and regularity of the didactics set simplifies the implementation by making the execution of many of the instruction classes similar. Later using the ALU, the actions required to complete various educational activity classes differ. A memory-reference instruction volition need to access the memory. For a load instruction, a retention read has to be performed. For a shop instruction, a retentivity write has to be performed. An arithmetic/logical education must write the data from the ALU back into a register. A load instruction too has to write the data fetched form retentiveness to a annals. Lastly, for a branch pedagogy, nosotros may need to alter the adjacent instruction accost based on the comparison. If the condition of comparing fails, the PC should be incremented by 4 to get the address of the side by side instruction. If the condition is true, the new address volition have to updated in the PC. Figure 8.ii below gives an overview of the CPU.

However, wherever we take 2 possibilities of inputs, we cannot join wires together.

We have to use multiplexers every bit indicated below in Figure eight.3.

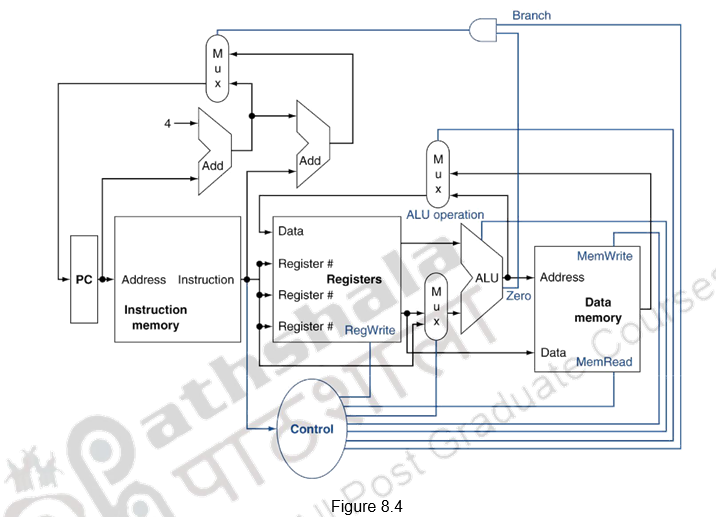

We likewise need to include the necessary command signals. Figure 8.4 below shows the datapath, likewise as the control lines for the major functional units. The control unit of measurement takes in the pedagogy equally an input and determines how to set the command lines for the functional units and two of the multiplexors. The 3rd multiplexor, which determines whether PC + four or the branch destination address is written into the PC, is set up based on the zero output of the ALU, which is used to perform the comparison of a branch on equal teaching. The regularity and simplicity of the MIPS instruction ready means that a elementary decoding process tin exist used to determine how to set the command lines.

Just to give a brief section on the logic design nuts, all of you know that information is encoded in binary as low voltage = 0, high voltage = 1 and in that location is one wire per bit. Multi-chip data are encoded on multi-wire buses. The combinational elements operate on data and the output is a function of input. In the case of state (sequential) elements, they shop information and the output is a function of both inputs and the stored data, that is, the previous inputs. Examples of combinational elements are AND-gates, XOR-gates, etc. An example of a sequential element is a register that stores data in a circuit. It uses a clock signal to make up one's mind when to update the stored value and is edge-triggered.

Now, we shall hash out the implementation of the datapath. The datapath comprises of the elements that process data and addresses in the CPU – Registers, ALUs, mux's, memories, etc. Nosotros volition build a MIPS datapath incrementally. We shall construct the basic model and keep refining it.

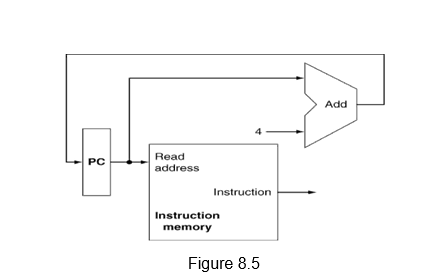

The portion of the CPU that carries out the instruction fetch operation is given in Figure 8.5.

As mentioned earlier, The PC is used to address the educational activity memory to fetch the educational activity. At the same time, the PC value is also fed to the adder unit of measurement and added with iv, and then that PC+four, which is the address of the next instruction in MIPS is written into the PC, thus making it ready for the next didactics fetch.

The next step is instruction decoding and operand fetch. In the instance of MIPS, decoding is done and at the aforementioned time, the register file is read. The processor's 32 general-purpose registers are stored in a construction chosen a annals file. A register file is a collection of registers in which any register tin be read or written by specifying the number of the register in the file.

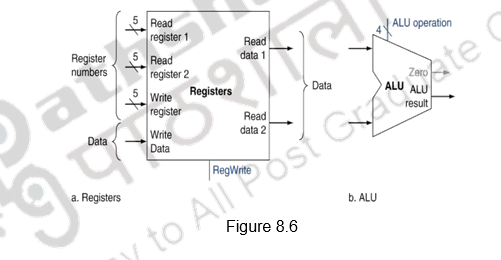

The R-format instructions have three register operands and we will demand to read two data words from the register file and write one data discussion into the register file for each teaching. For each data give-and-take to be read from the registers, we need an input to the annals file that specifies the register number to be read and an output from the annals file that volition deport the value that has been read from the registers. To write a data word, we will need two inputs- ane to specify the register number to be written and 1 to supply the data to be written into the register. The 5-bit register specifiers signal 1 of the 32 registers to be used.

The register file always outputs the contents of whatsoever register numbers are on the Read annals inputs. Writes, nevertheless, are controlled by the write control signal, which must be asserted for a write to occur at the clock edge. Thus, nosotros need a full of iv inputs (three for register numbers and one for data) and 2 outputs (both for data), as shown in Figure 8.six. The annals number inputs are v $.25 wide to specify one of 32 registers, whereas the information input and two data output buses are each 32 bits broad.

Subsequently the two annals contents are read, the next step is to laissez passer on these 2 data to the ALU and perform the required operation, equally decided by the command unit and the control signals. It might be an add together, decrease or any other type of operation, depending on the opcode. Thus the ALU takes ii 32-chip inputs and produces a 32-bit event, as well as a 1-bit bespeak if the result is 0. The control signals volition exist discussed in the next module. For now, nosotros wil assume that the appropriate control signals are somehow generated.

The same arithmetics or logical performance with an immediate operand and a register operand, uses the I-type of educational activity format. Here, Rs forms one of the source operands and the immediate component forms the second operand. These two volition take to be fed to the ALU. Before that, the xvi-bit firsthand operand is sign extended to form a 32-flake operand. This sign extension is washed by the sign extension unit.

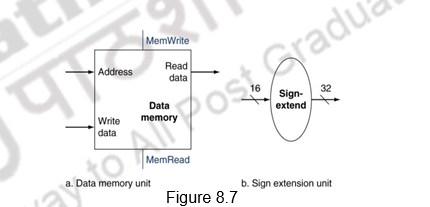

Nosotros shall next consider the MIPS load discussion and shop word instructions, which have the general form lw $t1,offset_value($t2) or sw $t1,offset_value ($t2). These instructions compute a memory address past calculation the base register, which is $t2, to the 16-bit signed kickoff field independent in the instruction. If the pedagogy is a store, the value to be stored must also be read from the register file where it resides in $t1. If the instruction is a load, the value read from memory must be written into the annals file in the specified register, which is $t1. Thus, we will need both the annals file and the ALU. In addition, the sign extension unit will sign extend the 16-chip start field in the instruction to a 32-fleck signed value. The next performance for the load and shop operations is the information memory admission. The data retentivity unit of measurement has to be read for a load instruction and the data memory must be written for store instructions; hence, it has both read and write control signals, an address input, too every bit an input for the data to exist written into retention. Figure 8.7 above illustrates all this.

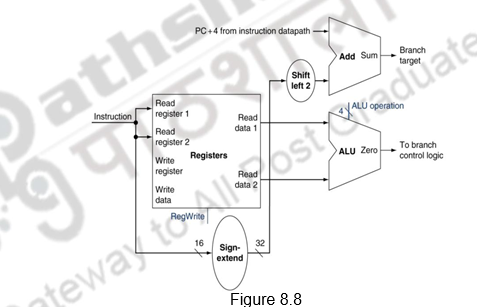

The branch on equal instruction has three operands, two registers that are compared forequality, and a xvi-bit offset used to compute the branch target accost, relative to the co-operative instruction address. Its course is beq $t1, $t2, offset. To implement this instruction, we must compute the branch target accost by adding the sign-extended offset field of the instruction to the PC. The teaching prepare compages specifies that the base for the co-operative address calculation is the address of the instruction post-obit the co-operative. Since nosotros accept already computed PC + iv, the address of the side by side instruction, in the instruction fetch datapath, information technology is easy to utilise this value as the base for calculating the co-operative target accost. Also, since the give-and-take boundaries have the two LSBs as zeros and branch target addresses must offset at word boundaries, the offset field is shifted left 2 bits. In addition to calculating the branch target accost, we must also determine whether the next instruction is the instruction that follows sequentially or the teaching at the branch target address. This depends on the condition being evaluated. When the condition is true (i.e., the operands are equal), the branch target address becomes the new PC, and we say that the branch is taken. If the operands are non equal, the incremented PC should supercede the current PC (just as for any other normal instruction); in this instance, we say that the branch is non taken.

Thus, the branch datapath must do two operations: compute the branch target address and compare the register contents. This is illustrated in Figure 8.8. To compute the branch target accost, the co-operative datapath includes a sign extension unit and an adder. To perform the compare, we demand to use the register file to supply the 2 register operands. Since the ALU provides an output signal that indicates whether the result was 0, we tin can send the 2 register operands to the ALU with the control set to do a subtract. If the Zip signal out of the ALU unit is asserted, nosotros know that the ii values are equal. Although the Zero output always signals if the outcome is 0, we will be using it merely to implement the equal exam of branches. Later, we will show exactly how to connect the command signals of the ALU for use in the datapath.

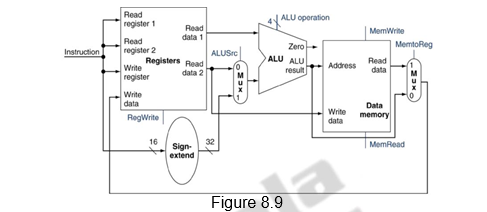

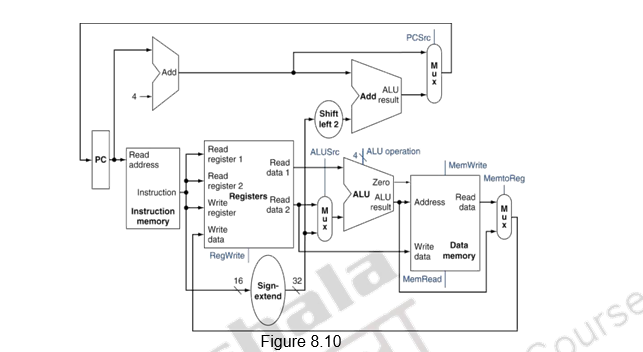

Now, that nosotros have examined the datapath components needed for the individual teaching classes, we can combine them into a unmarried datapath and add the control to consummate the implementation. The combined datapath is shown Figure 8.9 below.

The simplest datapath might attempt to execute all instructions in one clock wheel. This means that no datapath resource tin can exist used more than once per instruction, then whatever element needed more than one time must be duplicated. We therefore need a memory for instructions separate from one for information. Although some of the functional units will demand to be duplicated, many of the elements tin be shared by different pedagogy flows. To share a datapath element betwixt 2 different teaching classes, we may need to allow multiple connections to the input of an element, using a multiplexor and control indicate to select amidst the multiple inputs. While calculation multiplexors, we should notation that though the operations of arithmetic/logical ( R-type) instructions and the retention related instructions datapath are quite similar, in that location are sure key differences.

- The R-type instructions use ii register operands coming from the annals file. The memory instructions also use the ALU to do the address calculation, merely the 2d input is the sign-extended 16-bit first field from the educational activity.

- The value stored into a destination annals comes from the ALU for an R-type teaching, whereas, the data comes from retentiveness for a load.

To create a datapath with a common annals file and ALU, nosotros must support 2 different sources for the second ALU input, too every bit 2 different sources for the data stored into the register file. Thus, one multiplexor needs to exist placed at the ALU input and another at the data input to the register file, as shown in Figure 8.x.

Nosotros have discussed the private instructions – arithmetic/logical, memory related and branch. Now we can combine all the pieces to make a unproblematic datapath for the MIPS architecture past adding the datapath for educational activity fetch, the datapath from R-type and retentivity instructions and the datapath for branches. Figure beneath shows the datapath we obtain by combining the separate pieces. The branch instruction uses the main ALU for comparison of the annals operands, so we must keep the adder shown before for computing the branch target accost. An additional multiplexor is required to select either the sequentially following education address, PC + iv, or the branch target address to be written into the PC.

To summarize, nosotros have looked at the steps in the execution of a consummate instruction with MIPS as a case study. Nosotros have incrementally synthetic the datapath for the Arithmetic/logical instructions, Load/Store instructions and the Co-operative pedagogy. The implementation of the spring pedagogy to the datapath and the control path implementation will be discussed in the next module.

Web Links / Supporting Materials

- Computer Organization and Design – The Hardware / Software Interface, David A. Patterson and John L. Hennessy, quaternary.Edition, Morgan Kaufmann, Elsevier, 2009.

- Figurer Organisation, Carl Hamacher, Zvonko Vranesic and Safwat Zaky, 5th.Edition, McGraw- Loma Higher Education, 2011.

What Is Difference Between Datapath And Control Path,

Source: https://www.cs.umd.edu/~meesh/411/CA-online/chapter/execution-of-a-complete-instruction-datapath-implementation/index.html

Posted by: barnhartvishadep.blogspot.com

0 Response to "What Is Difference Between Datapath And Control Path"

Post a Comment